Replies

Welcome, guest

Join CrazyEngineers to reply, ask questions, and participate in conversations.

CrazyEngineers powered by Jatra Community Platform

-

@silverscorpion-iJKtdQ • Mar 25, 2011

Well, both latches and flip-flops are circuits whose output depends on the inputs and the previous outputs..

But the difference is that, a flip-flop will have a clock signal but a latch won't. In other words, latches are used in asynchronous circuits and flip-flops in synchronous circuits.

So, a flip-flop is nothing but a clocked latch! 😀 -

@the-redeemer-PEYjDR • Mar 26, 2011

Latches are level sensitive while flip flops are edge sensitive. -

@cranky-E9J79q • Mar 26, 2011

@silver scorpion,redeemer:so how does a latch work..by saying level triggered,what do we mean?Where does the value change in a latch? -

@the-redeemer-PEYjDR • Mar 26, 2011

Hi Cranky,

By level sensitive we mean that output will respond to change in input as long as the control signal is high. Control signal can be a clock in case of flip flop or any other asynchronous signal in case of latch.

By edge sensitive we mean that output will only respond to input at the point when the control signal goes to high from low. Now when the control signal is high the output will not change with change in input. It will again change at the next rising edge of the clock.

-

@cranky-E9J79q • Mar 27, 2011

@Redeemer:So what you mean is,when it is high,the output=input?...so where does it get latched?😐 -

@the-redeemer-PEYjDR • Mar 27, 2011

@Cranky

True in case of D latch but not in other latches , take for example the SR latch. In SR latch the latching will take place when the control signal is zero and when the control signal is one the output will change according to the previous values of output and the SR value.

Control S R Q Q'

0 0 0 latch latch

0 0 1 latch latch

0 1 0 latch latch

0 1 1 latch latch

1 0 0 latch latch

1 0 1 0 1

1 1 0 1 0

1 1 1 0 0

@Moderator

Why can't I upload images from my computer? -

@chetan-mehra-ZJKbfC • Mar 28, 2011

to all,

my question is:if we take a close look on the k-map simplification for the D flip flop,we see that the output does not depend on the previous outputs, but still we call it a flip flop,why? -

@silverscorpion-iJKtdQ • Mar 29, 2011

Hmm.. Yeah. The output will not depend on the previous input.

In any flip flop or latch, the 'current' output will depend on the 'previous' outputs and the 'current' inputs only. Not on previous inputs..

Is it clear? -

@cranky-E9J79q • May 9, 2011

@above all:thanks

Q2:How to start problems that involve designing a counter with frequency/2,f/3 etc. -

@avishkar-gote-TMS2ZE • May 10, 2011

Latch is a another term used for flip-flop.Latches are level sensitive while flip flops are edge sensitive and yes both latches and flip-flops are circuits whose output depends on the inputs and the previous outputs.. -

@raunak1302-Lfxh1a • Mar 13, 2012

What do we exactly mean by getting latched??cranky@Redeemer:So what you mean is,when it is high,the output=input?...so where does it get latched?😐 -

@sandeepbangalore-8NX9Eg • Mar 13, 2012

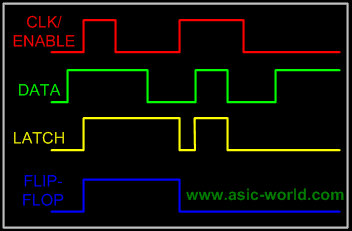

The example shows D-latch and D-FF.

The simplest form of data storage is latch. It's output responds immidiately to changes at the input and the input state will be remembered, or "latched" onto. While "enable" input is active the input of the latch is transparant to the output, once "enable" is disactivated the output remains locked. Flip-flops use clock as a control input. The transition on output Q occurs only at the edge of the clock pulse. Input data must present T_setup time before clock edge and remain T_hold time after.

* RESET input, while it is not shown, is present in most FF.

ex: flipflop :

module DFF (Q,_Q,D,clk,rst);

output Q,_Q;

input D,clk,rst;

reg Q,_Q;

always @(posedge clk or posedge rst)

begin

if (rst) Q <= 0;

else Q <= D;

_Q <= !Q;

end

endmodule

*****************************************************************

ex: latch :

module DLatch (Q,_Q,D,en,rst);

output Q,_Q;

input D,en,rst;

reg Q,_Q;

always @(en or D or posedge rst)

begin

if (rst) Q <= 0;

else if (en) Q <= D;

_Q <= !Q;

end

endmodule

*************************************************************

-

@sandeepbangalore-8NX9Eg • Mar 13, 2012

@#-Link-Snipped-#

Raunak1302What do we exactly mean by getting latched??