Standford Researchers Develop ‘High-Rise’ Chip By Using CNT Logic And RRAM Memory

@sharvari-panchbhai-JOvYc6

•

Oct 24, 2024

Oct 24, 2024

1.5K

Heat dissipation from electronic devices such as laptops, mobiles, et al is a discernible issue for all of us. Even after the cell phone is switched off, some of the electricity leaks out of the silicon transistors that lead to the wastage of electricity. In order to solve this problem, researchers from Standford Universty tried to build a different type of ‘high-rise’ chip using logic and memory.

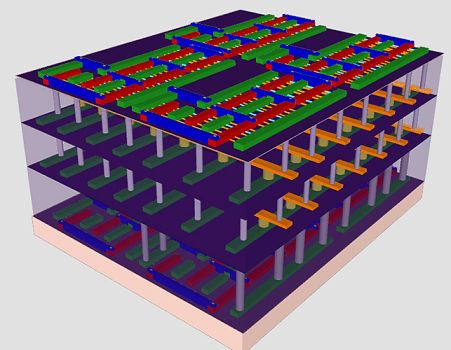

This chip comprises a tightly interconnected layers of carbon nanotubes transistors (CNT) on a very small area. It moves the data swiftly between the layers by using very less electricity. The team developed the CNTs on round quartz wafers and then moved the entire crop off the quartz onto a silicon wafer that became the foundation of high rise chip. While building CNT layer on quartz wafer, each layer was fabricated with adequate density in order to make the chip a high-performance logic device.

Creating layers of CNT transistors is just one part of their research. As they wanted to create a chip that combines both logic and memory, they also developed a new type of memory directly connected to each layer of CNTs. They built the memory using titanium nitride, hafnium oxide and platinum that formed a metal/oxide/metal sandwich. H.S. Philip Wong, the Williard R. and Inez Kerr Bell Professor in Stanford's School of Engineering, designed this resistive random access memory (RRAM) that uses less energy leading to prolonged battery life in electronic devices.

Unlike traditional circuit cards, multiple connections between memory and each layer of CNT logic in the high-rise chip will avoid the traffic jams while performing any logic operations. The research is still in a nascent stage and is lead by Subhasish Mitra, Stanford associate professor of electrical engineering and computer science, and H.-S. Philip Wong. The research paper about the architecture of this high-rise chip is being presented at IEEE International Electron Devices Meeting, December 15-17.

Source: #-Link-Snipped-#

This chip comprises a tightly interconnected layers of carbon nanotubes transistors (CNT) on a very small area. It moves the data swiftly between the layers by using very less electricity. The team developed the CNTs on round quartz wafers and then moved the entire crop off the quartz onto a silicon wafer that became the foundation of high rise chip. While building CNT layer on quartz wafer, each layer was fabricated with adequate density in order to make the chip a high-performance logic device.

Creating layers of CNT transistors is just one part of their research. As they wanted to create a chip that combines both logic and memory, they also developed a new type of memory directly connected to each layer of CNTs. They built the memory using titanium nitride, hafnium oxide and platinum that formed a metal/oxide/metal sandwich. H.S. Philip Wong, the Williard R. and Inez Kerr Bell Professor in Stanford's School of Engineering, designed this resistive random access memory (RRAM) that uses less energy leading to prolonged battery life in electronic devices.

Unlike traditional circuit cards, multiple connections between memory and each layer of CNT logic in the high-rise chip will avoid the traffic jams while performing any logic operations. The research is still in a nascent stage and is lead by Subhasish Mitra, Stanford associate professor of electrical engineering and computer science, and H.-S. Philip Wong. The research paper about the architecture of this high-rise chip is being presented at IEEE International Electron Devices Meeting, December 15-17.

Source: #-Link-Snipped-#