General Machine Structure - Von neumann Architecture Explained - System Programming

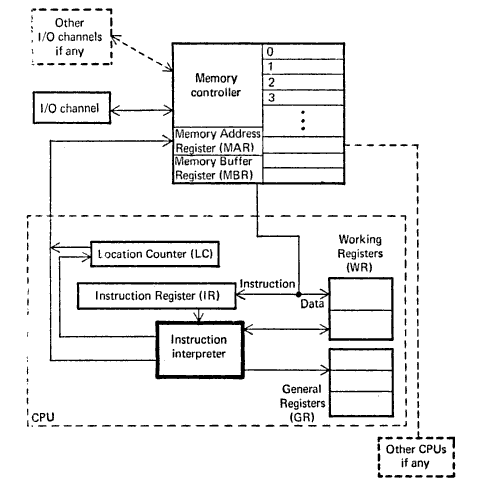

The structure of CPU for a typical Von Neumann Machine is as follows -

[Image Courtesy - Donovan Book]

The structure above consists of -

1. Instruction Interpreter

2. Location Counter

3. Instruction Register

4. Working Registers

5. General Register

The Instruction Interpreter Hardware is basically a group of circuits that perform the operation specified by the instructions fetched from the memory.

The Location Counter can also be called as Program/Instruction Counter simply points to the current instruction being excuted.

The working registers are often called as the "scratch pads" because they are used to store temporary values while calculation is in progress.

This CPU interfaces with Memory through MAR & MBR

MAR (Memory Address Register) - contains address of memory location (to be read from or stored into)

MBR (Memory Buffer Register) - contains copy of address specified by MAR

Memory controller is used to transfer data between MBR & the memory location specified by MAR

The role of I/O Channels is to input or output information from memory.

You may discuss this further in this thread.

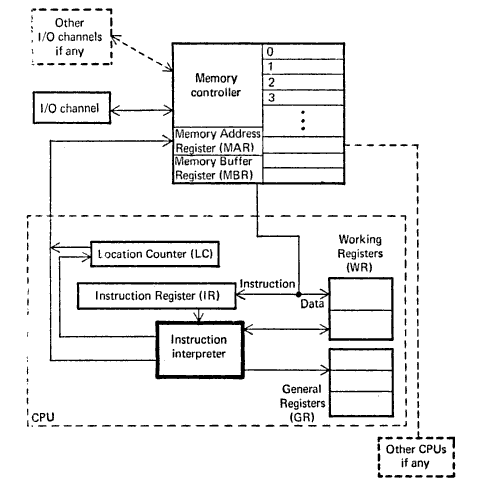

[Image Courtesy - Donovan Book]

The structure above consists of -

1. Instruction Interpreter

2. Location Counter

3. Instruction Register

4. Working Registers

5. General Register

The Instruction Interpreter Hardware is basically a group of circuits that perform the operation specified by the instructions fetched from the memory.

The Location Counter can also be called as Program/Instruction Counter simply points to the current instruction being excuted.

The working registers are often called as the "scratch pads" because they are used to store temporary values while calculation is in progress.

This CPU interfaces with Memory through MAR & MBR

MAR (Memory Address Register) - contains address of memory location (to be read from or stored into)

MBR (Memory Buffer Register) - contains copy of address specified by MAR

Memory controller is used to transfer data between MBR & the memory location specified by MAR

The role of I/O Channels is to input or output information from memory.

You may discuss this further in this thread.

0